Definition & Role

Random Access Memory (RAM) is a volatile memory that temporarily stores data and instructions while a computer is running. It acts as the CPU’s workspace, enabling fast access to information needed for active processes. Unlike permanent storage such as hard drives or SSDs, RAM loses its content when power is turned off. Its size and speed directly affect system performance and multitasking capability.

Types & Caching Tiers

| Memory Type | Volatility | Typical Use Case | Characteristics |

|---|---|---|---|

| DRAM (Dynamic RAM) | Volatile | Main system memory | High density, low cost, requires refresh cycles |

| SRAM (Static RAM) | Volatile | CPU caches (L1/L2/L3) | Very fast, no refresh needed, low density, expensive |

| eDRAM (Embedded DRAM) | Volatile | On-die cache, specialized processors | Faster than external DRAM, integrated into chip |

| MRAM (Magnetoresistive RAM) | Nonvolatile | Emerging memory tech | Stores data via magnetic states, retains info without power |

| ReRAM (Resistive RAM) | Nonvolatile | Experimental systems, embedded devices | Stores data via resistance changes, promising for future use |

Key Technical Parameters

- Capacity: DDR3 (up to 8 GB/module), DDR4 (up to 64 GB), DDR5 (up to 256 GB), DDR6 (512 GB+ projected)

- Data Rate: DDR3 (800–2133 MT/s), DDR4 (1600–3200+), DDR5 (4800–8800+), DDR6 (up to 17600 MT/s)

- Bandwidth: DDR3 (~17 GB/s), DDR4 (~25.6 GB/s), DDR5 (~38–70+ GB/s), DDR6 (70–140+ GB/s)

- Latency: DDR3 has lower CAS latency (CL9–11), DDR4/5/6 have higher CL but similar real latency (~13–15 ns)

- Voltage: DDR3 (1.5V), DDR4 (1.2V), DDR5 (1.1V), DDR6 (~1.0V or lower)

- ECC: Optional in DDR3/DDR4, on-die ECC in DDR5/6

- Power Management: DDR5/6 include PMIC on DIMM for better efficiency

- Topology: DDR5 introduces dual 32-bit subchannels and more bank groups for parallelism

Modules, Controllers, and Topology

- Modules: UDIMM, RDIMM, LRDIMM, SO-DIMM, NVDIMM

- Controllers: Integrated in CPU/SoC; define supported DDR version, channels, ECC, and density

- Topology: DDR3/4 use single-ended/fly-by routing; DDR5/6 support advanced interleaving and multi-rank parallelism

- Interconnects: CXL enables memory pooling and coherent access across CPUs and accelerators

Process, Packaging, and Manufacturing

- Process Nodes: DRAM scaling is independent of logic nodes; density improves with each generation

- Packaging: DDR5/6 use advanced PCB layouts; HBM uses TSVs and interposers (CoWoS, Foveros)

- PMIC: DDR5/6 DIMMs include power management ICs for voltage regulation

- Vendors: Samsung, SK Hynix, Micron lead DRAM manufacturing; Corsair, Kingston, G.Skill produce modules

Performance Tradeoffs and Selection Guidance

| Use Case | Recommended RAM |

| Gaming/Desktop | DDR4 (3200 MT/s) or DDR5 (6000+ MT/s); dual/quad channel kits for bandwidth |

| Content Creation | DDR4/DDR5 with high capacity (32–128 GB), ECC optional |

| AI/HPC Training | DDR5 with many channels, HBM for accelerators, CXL for pooling |

| Mobile Devices | LPDDR5/5X/6 for bandwidth per watt; SoC tuning critical |

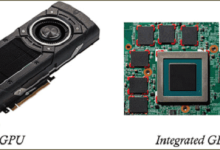

| GPUs | GDDR6/6X for consumer cards; HBM for AI/HPC GPUs |

| Servers | ECC RDIMM/LRDIMM, NUMA-aware layout, DDR5 scaling with CXL |

Technology Trends (2023–2026)

- DDR5 mainstreaming: Higher speeds, PMIC, on-die ECC

- DDR6 development: Doubling bandwidth, more bank groups, lower voltage

- LPDDR6: Mobile DRAM pushing bandwidth per watt

- HBM3 adoption: AI accelerators and chiplet GPUs

- CXL memory pooling: Disaggregated memory architectures

- Advanced packaging: 2.5D/3D stacking, chiplet DRAM islands

Diagnostics, tuning and reliability concerns

- Memory training & timing: XMP/EXPO profiles for consumer modules; manual timing tuning can improve latency/throughput.

- Error modes: Soft errors (cosmic rays) mitigated by ECC; wear and retention issues mostly in DRAM refresh management and thermal stress.

- Testing: Memtest-type stress testing, server DIMM validation, memory channel stress tests reveal marginal stability at high frequencies.

- Replacement lifecycle: DRAM generally long‑lived; failures more often from system/board issues or early infant mortality.

DDR3 vs DDR4 vs DDR5 vs DDR6 — Full Comparison

| Feature | DDR3 | DDR4 | DDR5 | DDR6 (early specs) |

| Launch Year | ~2007 | ~2014 | ~2020 | ~2025–2026 (expected) |

| Voltage | 1.5V (1.35V for DDR3L) | 1.2V | 1.1V | ~1.0V or lower |

| Data Rate (MT/s) | 800–2133 | 1600–3200+ | 4800–8800+ | 8800–17600+ (target) |

| Bandwidth (GB/s per channel) | ~12–17 | ~25.6 | ~38.4–70+ | 70–140+ (projected) |

| Prefetch | 8n | 8n | 16n | 16n |

| Bank Groups | No | Yes (4) | Yes (8) | Yes (more, TBD) |

| On-DIMM Power Mgmt | No | No | Yes (PMIC on module) | Yes |

| ECC Support | Optional | Optional | On-die ECC + external ECC | On-die ECC |

| Module Pins | 240 (DIMM) | 288 (DIMM) | 288 (new layout) | TBD |

| Latency (ns) | ~13–15 | ~13–15 | ~14–18 | TBD (likely similar) |

| Density per DIMM | Up to 8 GB | Up to 64 GB | Up to 256 GB | 512 GB+ (future) |

Performance & Use Cases

| Use Case | DDR3 | DDR4 | DDR5 | DDR6 |

| Legacy PCs / Embedded | ✅ | ⚠️ | ❌ | ❌ |

| Mainstream PCs | ⚠️ | ✅ | ✅ | ⚠️ (future) |

| Gaming / High-End | ❌ | ✅ | ✅✅ | ✅ (future GPUs/CPUs) |

| Servers / Workstations | ⚠️ | ✅ | ✅✅ | ✅ (planned) |

| AI / HPC | ❌ | ⚠️ | ✅ (with HBM) | ✅ (with CXL/Chiplets) |

-=||=-FavoriteLike (0)

Must log in before commenting!

Sign In Sign Up